# Layout-Optimization of Power-Devices

Frederik Vanaverbeke, J. Das, H. Oprins, J. Derluyn, M. Germain, W. De Raedt

#### Outline

- 2. Unit gatewidth

- 3. Thermal

- 4. Number of unit cells

- 5. EM-simulations

#### Outline

- 2. Unit gatewidth

- 3. Thermal

- 4. Number of unit cells

- **5.** EM-simulations

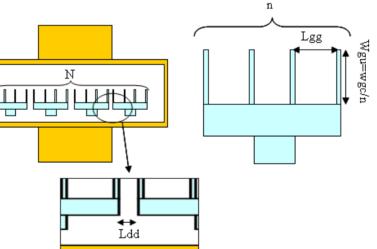

# Problem Description + Nomenclature

- A device = Nunit cells, each having ngate-fingers of length Nggg

- Total gatewidth is  $W = N \times n \times W_{gu}$ . And  $W \sim Pout$

- $\log$  = finger spacing

Unit-Cell

?: How to choose N,n,w<sub>gu</sub>,L<sub>gg</sub>,

-> EM effects

-> Thermal effects

- 2. Unit gatewidth  $W_{gu}$

- 3. Thermal

- 4. Number of unit cells

- **5.** EM-simulations

# Unit gatewidth Wgu

- IDS modulation: UNIFORM over the gate finger

- => Phase rotation & hence length must be limited.

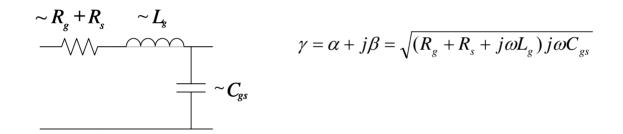

- Finger ~ transmission line

- voltage:

$$v(x,s) = \frac{Z_0(s)E_G(s)}{Z_0(s) + Z_G(s)} \cdot \frac{e^{-\gamma(s)x} + \Gamma_L(s)e^{-\gamma(s)(2L-x)}}{1 - \Gamma_L(s)\Gamma_G(s)e^{-\gamma(s)2L}}$$

- difference in phase between v(0,s) and  $v(w_{gu},s) < \pi/16$  imposes a limit to  $W_{gu}$

- $\gamma$  (complex number):

- Through simulation

- By modeling an infinitesimal section of the line

# Unit gatewidth Wgu

- γ (complex number):

- Through simulation in Ansoft's HFSS

- Infinitesimal section of the line; values from transistor extractions

• Resulting maximum values for  $W_{qu}$  in  $\mu$ m:

|       | HFSS | Extractions |

|-------|------|-------------|

| 2GHz  | 368  | 298         |

| 5GHz  | 236  | 188         |

| 10GHz | 165  | 130         |

- 2. Unit gatewidth  $w_{gu}$

- 3. Thermal *Lgg*

- 4. Number of unit cells

- **5.** EM-simulations

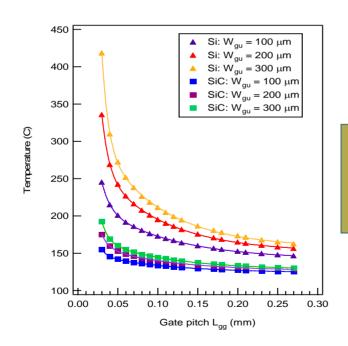

# Thermal Lgg

From a previous Imec study

[J. Das et. Al, IEEE Trans. Electron Devices, 53 (11), pp. 2696-2702,2006]

Relationship Lgg, Temperature and W<sub>gu</sub> by means of 3D-simulations:

Limiting the temperature to 160 °C imposes a minimum to  $L_{qq}$  for a certain  $w_{qu}$

The longer the finger, the further they have to be separated from each other

- 2. Unit gatewidth *w*<sub>gu</sub>

- 3. Thermal *Lgg*

- 4. Number of unit cells N (and n)

- **5.** EM-simulations

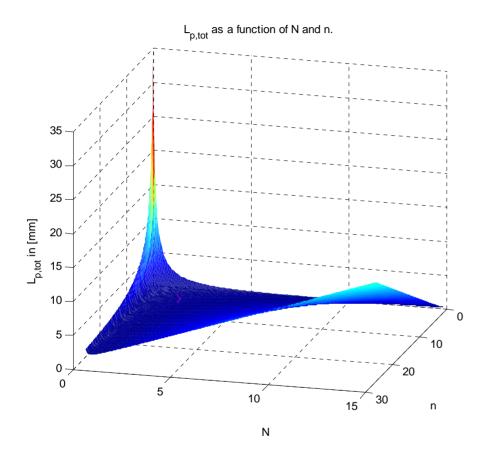

## Number of unit cells N (and n)

Choose that combination of N, n and *w*<sub>gu</sub> that minimizes the chip area through

$$L_{p} = \frac{N}{2}(n-1)L_{gg} + \frac{w_{g}}{N \cdot n} + \frac{N-1}{2}L_{dd}$$

- ... taking into account

- *N* is integer and *n* is even

- *w<sub>gu</sub>* has a maximum

a minimum number of fingers is necessary

*N x n* has a minimum value

- The cells are measurable by probes

=> N has a minimum value

- => Graphical method

# Number of unit cells *N* (and *n*)

- 1. Projection of *Lp* on N,n-plane

- Plot the discrete working grid (cyan diamonds)

- 3.  $w_{gu}$  has maximum  $N \times n$  is minimum~hyperbole

- 4. On-wafer characterization Minimum value for *N*

- 5. Pick that point in the working area, where  $L_p$  is minimal.

#### imec

- 2. Unit gatewidth  $w_{gu}$

- 3. Thermal *Lgg*

- **4.** Number of unit cells *N* (and *n*)

- 5. EM-simulations

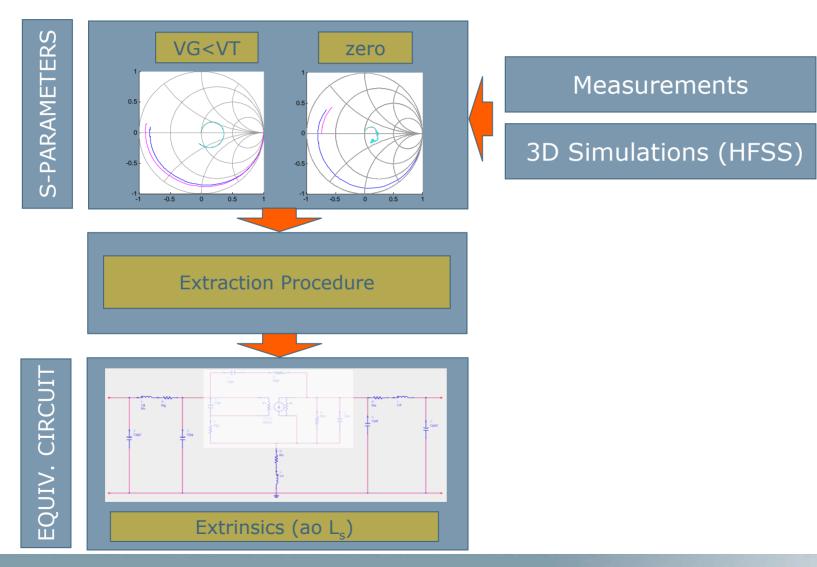

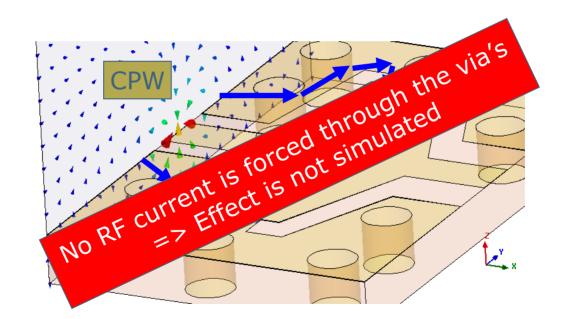

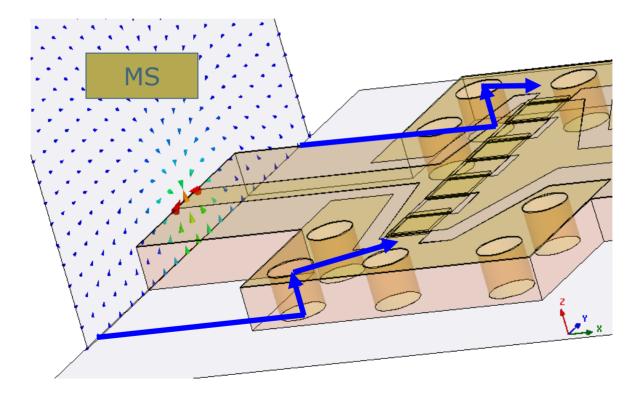

• Devices in Microstrip Packages

Gate,Source,Drain on top of die (CPW)

<->

Ground=bottom of MS Package

- Source-areas connected to bottom of MS Package:

- Wirebonds

- Via's

- Source-Inductance kills performance

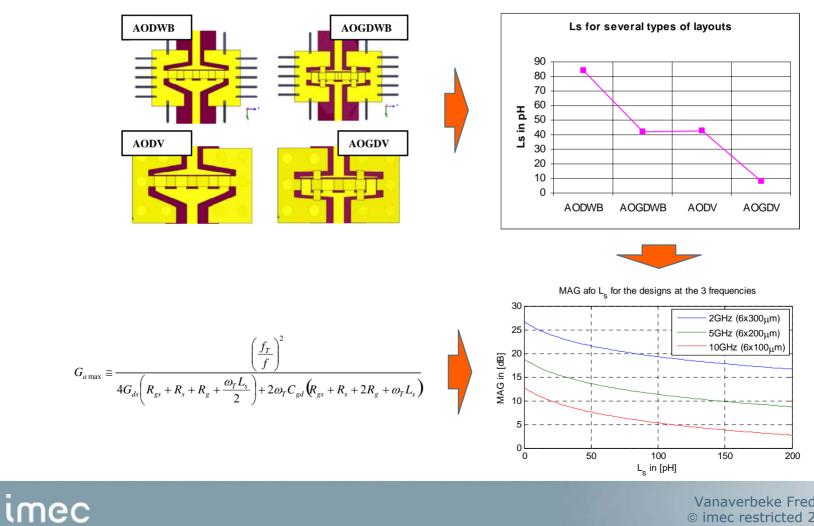

• Approximation of MAG:

$$G_{a\max} \cong \frac{\left(\frac{f_T}{f}\right)^2}{4G_{ds}\left(R_{gs} + R_s + R_s + \frac{\omega_T L_s}{2}\right) + 2\omega_T C_{gd}\left(R_{gs} + R_s + 2R_g + \omega_T L_s\right)}$$

L<sub>s</sub> should be minimized

- L<sub>s</sub> doesn't scale and is not predictable

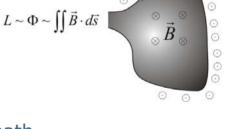

- Any L is proportional with area of membrane of mag flux

- Surface is difficult to determine because

- *More* than 1 via's or WB's (+ coupling)

- Common for the gate-source path and drain-source path

- Airbridges

- => EM-simulations

#### imec

Effect of via's <=> they conduct RF Current Excitation of waveports is key

Effect of via's <=> they conduct RF Current Excitation of waveports is key

#### Applied to 4 configurations

Vanaverbeke Frederik © imec restricted 2008

# aspire invent achieve