# Geometrical Effect Analysis on $f_T$ and $f_{max}$ of 0.18 $\mu m$ SiGe HBT

#### By

Ping-Chun Yeh, Chih-Hung Hsieh, Chwan-Ying Lee\*, Yu-Lin Chu\*, Kuan-Lun Chang\*, Denny Tang \*, John Chern\* and Hwann-Kaeo Chiou.

Department of Electrical Engineering

National Central University, Taiwan

\*Taiwan Semiconductor Manufacturing Company

#### **Outline**

- 0.18 μm SiGe power cell design

- Power cell analysis

I<sub>c</sub>- V<sub>CE</sub> Curves

**Forward Gummel plot**

Parallel plate Capacitor on Dielectric substrate

**Back-End 3D-EM simulation**

**Device**  $f_T$  and  $f_{max}$

**Transit time extraction**

**Devices performance comparison**

- Status

- Conclusion

### **Purpose**

- The purpose of this work is to analyze the geometrical effects of parameters  $f_T$  and  $f_{max}$  of 0.18  $\mu m$  high speed SiGe HBTs technology.

- The three unit-cell layout design are proposed to investigated the geometrical effect in this study.

- The standard unit-cell can be applied in power cell for power amplifier design.

## 0.18 µm SiGe power cell design

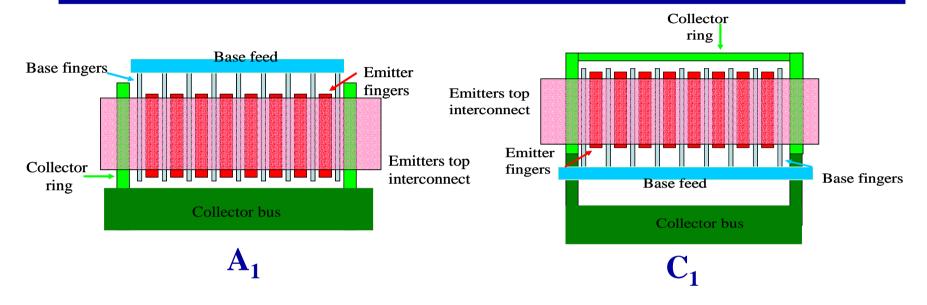

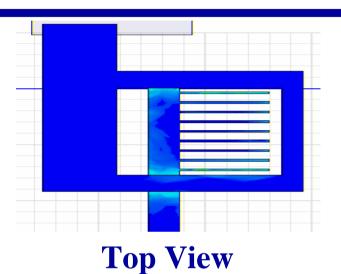

$\mathbf{B}_1$

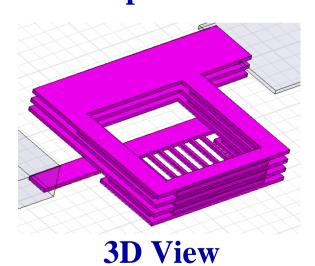

In  $A_1$  Structure, the base feed has no overlap with the collector trace In  $B_1$  Structure, the base fingers have overlap with the collector ring

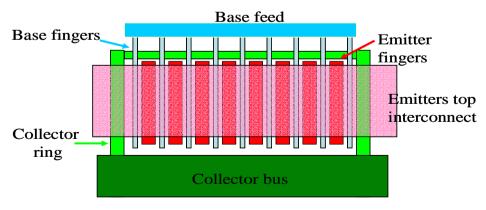

## Power cell analysis: I<sub>c</sub>- V<sub>CE</sub> Curves

$$I_b = 30 \mu A - 150 \mu A$$

$I_b = 60 \mu A - 300 \mu A$

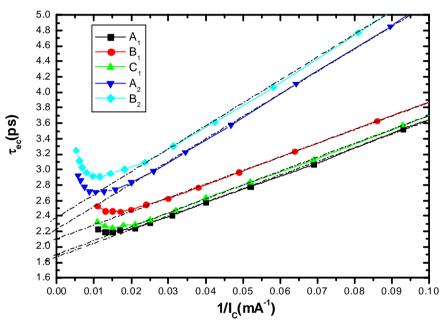

Measured I\_V curves for three devices  $(A_1, B_1, and C_1)$  and two devices  $(A_2 and B_2)$  demonstrate the similar dc performance.

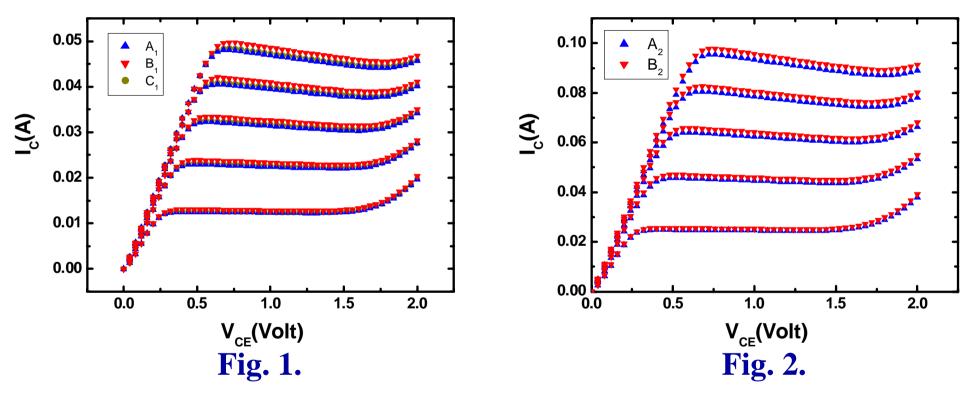

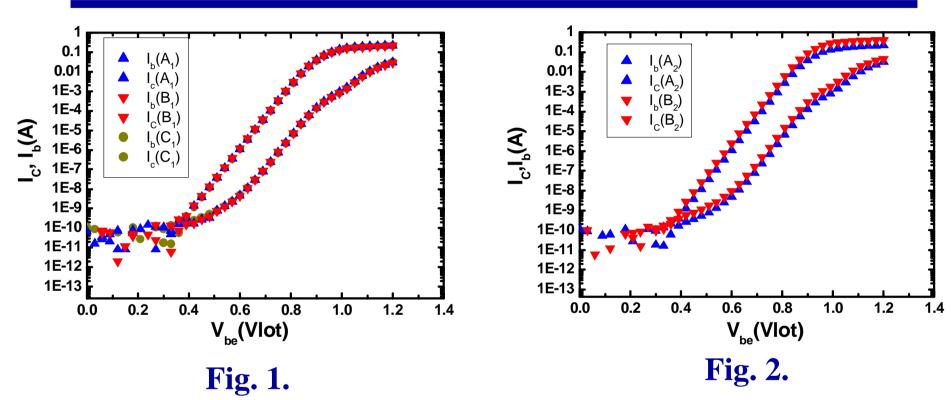

## Forward Gummel plot

Measured Forward Gummel plots ( $V_{BC} = 0.5$ V) for three devices ( $A_1$ ,  $B_1$ , and  $C_1$ ) and two devices ( $A_2$  and  $B_2$ ) demonstrate the similar dc performance.

#### National Central University

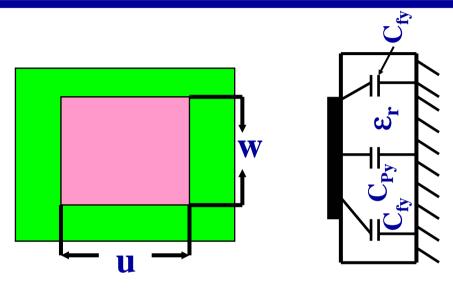

## **Parallel plate Capacitor on Dielectric substrate**

Total parallel plate capacitance

$$\longrightarrow C_{Total} = C_P + 2C_{fx} \times W + 2C_{fy} \times u \tag{1}$$

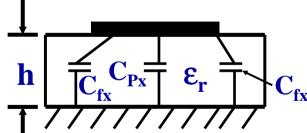

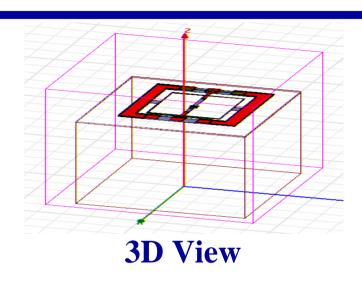

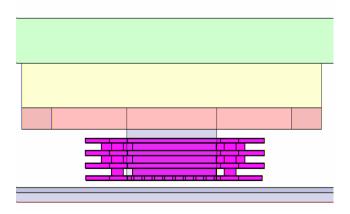

### **Back-End 3D-EM Simulation**

**Side View**

## **Back-End 3D-EM Simulation(cond't)**

## **Device** $f_T$ and $f_{max}$

#### Total emitter-collector delay time

$$\tau_{ec} = \tau_b + \tau_c + \frac{\eta KT}{qI_C} (C_{BE} + C_{BC}) + (R_E + R_C)C_{BC} = \frac{1}{2\pi f_T}$$

(1)

#### The well-known formula for maximum oscillation frequency

$$f_{\text{max}} = \sqrt{\frac{f_T}{8\pi R_{BB}C_{BC}}} \tag{2}$$

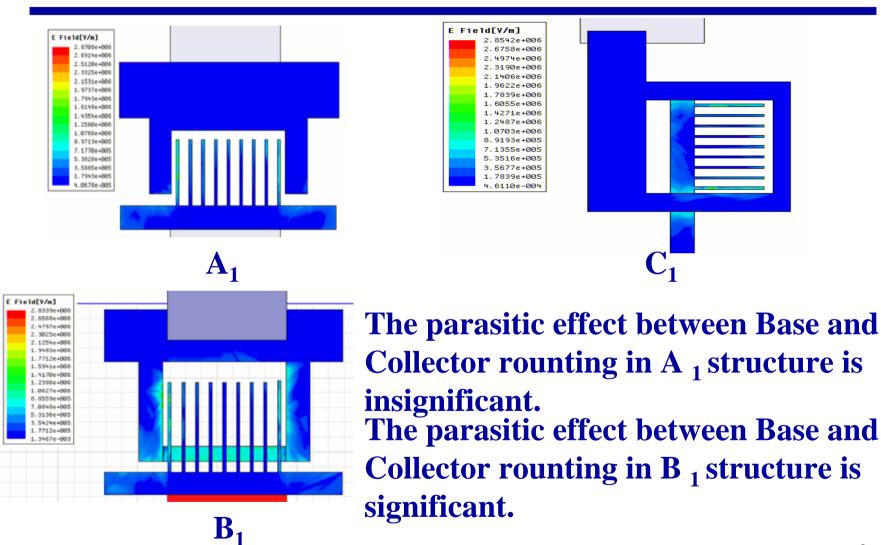

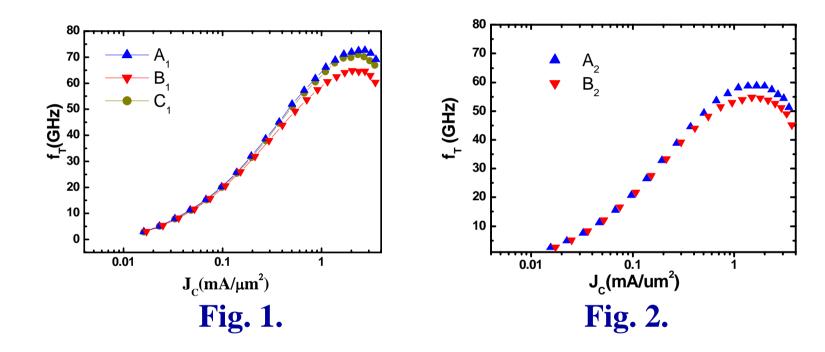

## **Device f**<sub>T</sub> **Performance**

Measured cutoff-frequency vs. collector current density.

## **Device f**<sub>max</sub> **Performance**

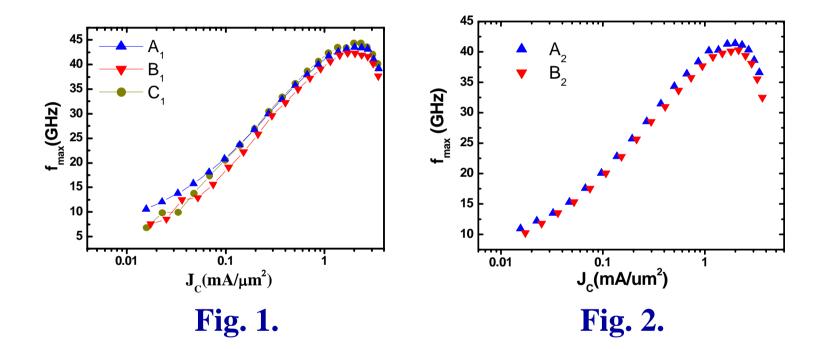

Measured maximum oscillation frequency vs. collector current density.

#### **Device transit time extraction**

| SiGe<br>HBTs                             | $\mathbf{A_1}$ | <b>B</b> <sub>1</sub> | C <sub>1</sub> | $\mathbf{A_2}$ | B <sub>2</sub> |

|------------------------------------------|----------------|-----------------------|----------------|----------------|----------------|

| $\frac{\tau_b + \tau_c}{(\mathbf{psc})}$ | 0.946          | 1.063                 | 0.935          | 1.153          | 1.374          |

Measured total emitter-collector delay time vs. inverse collector current.

$$\tau_b + \tau_c = \tau_{ec} - (R_E + R_C)C_{BC}$$

At Intercept Point (1)

**RC** Charging time

## Performance summaries of SiGe HBTs with different layouts

| SiGe<br>HBTs           | $\mathbf{A_1}$ | <b>B</b> <sub>1</sub> | C <sub>1</sub> | $\mathbf{A_2}$ | B <sub>2</sub> |

|------------------------|----------------|-----------------------|----------------|----------------|----------------|

| <b>Emitter fingers</b> | 8              | 8                     | 8              | 16             | 16             |

| Base<br>fingers        | 9              | 9                     | 9              | 18             | 18             |

| f <sub>T</sub> (GHz)   | 73             | 65                    | 71             | 59             | 55             |

| f <sub>max</sub> (GHz) | 43             | 41                    | 44             | 41             | 40             |

The perfromance of the  $f_T$  is significantly improved by 8 GHz higher for the slightly in layout arrangement.

## Device equivalent components of SiGe HBTs with different layouts

| SiGe<br>HBTs          | $\mathbf{A_1}$ | <b>B</b> <sub>1</sub> | C <sub>1</sub> | $\mathbf{A_2}$ | $\mathbf{B}_2$ |

|-----------------------|----------------|-----------------------|----------------|----------------|----------------|

| R <sub>BB</sub> (Ohm) | 11.68          | 11.09                 | 11.36          | 6.31           | 6.45           |

| R <sub>C</sub> (Ohm)  | 5.53           | 5.68                  | 5.58           | 3.53           | 3.46           |

| R <sub>E</sub> (Ohm)  | 1.19           | 1.23                  | 1.27           | 0.73           | 0.68           |

| C <sub>BC</sub> (fF)  | 139.12         | 148.45                | 141.3          | 247.15         | 255.84         |

Both  $A_2$  and  $B_2$  structures are almost scalable with  $A_1$  and  $B_1$  structures.

## Transit time analysis of SiGe HBTs with different layouts

|                                                                  | $\mathbf{A_1}$ | <b>B</b> <sub>1</sub> | $C_1$ | $\mathbf{A_2}$ | $\mathbf{B_2}$ |

|------------------------------------------------------------------|----------------|-----------------------|-------|----------------|----------------|

| SiGe<br>HBTs                                                     |                |                       |       |                |                |

| Intercept (psec)                                                 | 1.882          | 2.088                 | 1.903 | 2.208          | 2.435          |

| $(\mathbf{R_E} + \mathbf{R_C})\mathbf{C_{BC}}$ $(\mathbf{psec})$ | 0.936          | 1.025                 | 0.968 | 1.055          | 1.061          |

| $\tau_{\rm b} + \tau_{\rm c}  ({\rm psc})$                       | 0.946          | 1.063                 | 0.935 | 1.153          | 1.374          |

#### **Status**

The High Voltage standard unit-cell which can be applied in power cell for power amplifier design.

Current gain collapse for pitch= $2\mu m$  device. Selfheating for device with pitch= $2\mu m$  is much worse than that for device with pitch= $6\mu m$ .

#### **Conclusion**

- We have analyzed the geometrical effects of parameters  $f_T$  and  $f_{max}$  of 0.18  $\mu m$  high speed SiGe BiCMOS technology. The device scaling is feasible in the standard unit-cell.

- The key factor of the layout is the manner of overlap structure between the base fingers and collector traces. Although the smaller overlap of the base fingers in  $B_1$ , it gets proximity effect and eventually obtains more parasitic capacitances than those of  $C_1$  and  $A_1$ .

- The high frequency performances are related with the associated parasitic junction capacitances  $C_{BC}$  and  $\tau_b$  +  $\tau_c$ . The significantly improvement in  $f_T$  is obtained by considering the routes in base and collector.

- The standard unit-cell can be applied in power cell for power amplifier design.